DS003-2 (v2.5) April 2, 2001

# **Architectural Description**

# **Virtex Array**

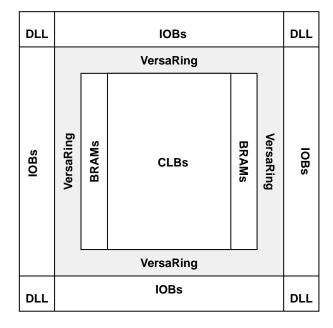

The Virtex user-programmable gate array, shown in Figure 1, comprises two major configurable elements: configurable logic blocks (CLBs) and input/output blocks (IOBs).

- CLBs provide the functional elements for constructing logic

- IOBs provide the interface between the package pins and the CLBs

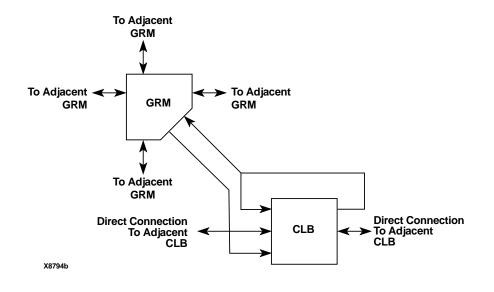

CLBs interconnect through a general routing matrix (GRM). The GRM comprises an array of routing switches located at the intersections of horizontal and vertical routing channels. Each CLB nests into a VersaBlock<sup>™</sup> that also provides local routing resources to connect the CLB to the GRM.

The VersaRing<sup>™</sup> I/O interface provides additional routing resources around the periphery of the device. This routing improves I/O routability and facilitates pin locking.

The Virtex architecture also includes the following circuits that connect to the GRM.

- Dedicated block memories of 4096 bits each

- Clock DLLs for clock-distribution delay compensation and clock domain control

- 3-State buffers (BUFTs) associated with each CLB that drive dedicated segmentable horizontal routing resources

Values stored in static memory cells control the configurable logic elements and interconnect resources. These values load into the memory cells on power-up, and can reload if necessary to change the function of the device.

# Input/Output Block

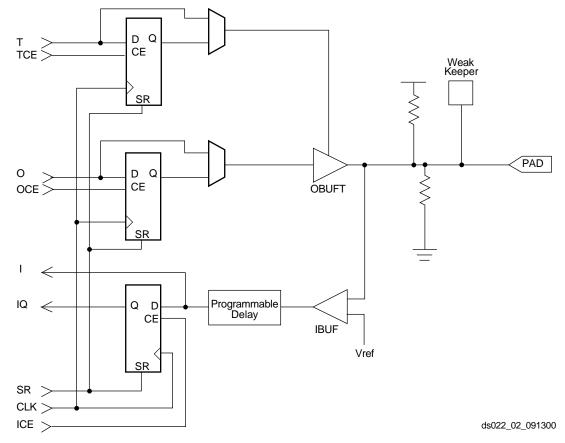

The Virtex IOB, Figure 2, features SelectIO<sup>™</sup> inputs and outputs that support a wide variety of I/O signalling standards, see Table 1.

The three IOB storage elements function either as edge-triggered D-type flip-flops or as level sensitive latches. Each IOB has a clock signal (CLK) shared by the three flip-flops and independent clock enable signals for each flip-flop.

In addition to the CLK and CE control signals, the three flip-flops share a Set/Reset (SR). For each flip-flop, this signal can be independently configured as a synchronous Set, a synchronous Reset, an asynchronous Preset, or an asynchronous Clear.

# Virtex<sup>™</sup> 2.5 V Field Programmable Gate Arrays

#### Product Specification

The output buffer and all of the IOB control signals have independent polarity controls.

vao\_b.eps

Figure 1: Virtex Architecture Overview

All pads are protected against damage from electrostatic discharge (ESD) and from over-voltage transients. Two forms of over-voltage protection are provided, one that permits 5 V compliance, and one that does not. For 5 V compliance, a Zener-like structure connected to ground turns on when the output rises to approximately 6.5 V. When PCI 3.3 V compliance is required, a conventional clamp diode is connected to the output supply voltage, V<sub>CCO</sub>.

Optional pull-up and pull-down resistors and an optional weak-keeper circuit are attached to each pad. Prior to configuration, all pins not involved in configuration are forced into their high-impedance state. The pull-down resistors and the weak-keeper circuits are inactive, but inputs can optionally be pulled up.

The activation of pull-up resistors prior to configuration is controlled on a global basis by the configuration mode pins. If the pull-up resistors are not activated, all the pins will float. Consequently, external pull-up or pull-down resistors must be provided on pins required to be at a well-defined logic level prior to configuration.

All Virtex IOBs support IEEE 1149.1-compatible boundary scan testing.

<sup>© 2001</sup> Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Figure 2: Virtex Input/Output Block (IOB)

| I/O Standard       | Input Reference<br>Voltage (V <sub>REF</sub> ) | Output Source<br>Voltage (V <sub>CCO</sub> ) | Board Termination<br>Voltage (V <sub>TT</sub> ) | 5 V Tolerant |

|--------------------|------------------------------------------------|----------------------------------------------|-------------------------------------------------|--------------|

| LVTTL 2 – 24 mA    | N/A                                            | 3.3                                          | N/A                                             | Yes          |

| LVCMOS2            | N/A                                            | 2.5                                          | N/A                                             | Yes          |

| PCI, 5 V           | N/A                                            | 3.3                                          | N/A                                             | Yes          |

| PCI, 3.3 V         | N/A                                            | 3.3                                          | N/A                                             | No           |

| GTL                | 0.8                                            | N/A                                          | 1.2                                             | No           |

| GTL+               | 1.0                                            | N/A                                          | 1.5                                             | No           |

| HSTL Class I       | 0.75                                           | 1.5                                          | 0.75                                            | No           |

| HSTL Class III     | 0.9                                            | 1.5                                          | 1.5                                             | No           |

| HSTL Class IV      | 0.9                                            | 1.5                                          | 1.5                                             | No           |

| SSTL3 Class I &II  | 1.5                                            | 3.3                                          | 1.5                                             | No           |

| SSTL2 Class I & II | 1.25                                           | 2.5                                          | 1.25                                            | No           |

| СТТ                | 1.5                                            | 3.3                                          | 1.5                                             | No           |

| AGP                | 1.32                                           | 3.3                                          | N/A                                             | No           |

#### Table 1: Supported Select I/O Standards

# Input Path

A buffer In the Virtex IOB input path routes the input signal either directly to internal logic or through an optional input flip-flop.

An optional delay element at the D-input of this flip-flop eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the FPGA, and when used, assures that the pad-to-pad hold time is zero.

Each input buffer can be configured to conform to any of the low-voltage signalling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage,  $V_{REF}$ . The need to supply  $V_{REF}$  imposes constraints on which standards can used in close proximity to each other. See **I/O Banking**, page 3.

There are optional pull-up and pull-down resistors at each input for use after configuration. Their value is in the range 50 k $\Omega$  – 100 k $\Omega$ .

# Output Path

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output signal can be routed to the buffer directly from the internal logic or through an optional IOB output flip-flop.

The 3-state control of the output can also be routed directly from the internal logic or through a flip-flip that provides synchronous enable and disable.

Each output driver can be individually programmed for a wide range of low-voltage signalling standards. Each output buffer can source up to 24 mA and sink up to 48mA. Drive strength and slew rate controls minimize bus transients.

In most signalling standards, the output High voltage depends on an externally supplied V<sub>CCO</sub> voltage. The need to supply V<sub>CCO</sub> imposes constraints on which standards can be used in close proximity to each other. See I/O Banking, page 3.

An optional weak-keeper circuit is connected to each output. When selected, the circuit monitors the voltage on the pad and weakly drives the pin High or Low to match the input signal. If the pin is connected to a multiple-source signal, the weak keeper holds the signal in its last state if all drivers are disabled. Maintaining a valid logic level in this way eliminates bus chatter.

Because the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate  $V_{REF}$  voltage must be provided if the signalling standard requires one. The provision of this voltage must comply with the I/O banking rules.

# I/O Banking

Some of the I/O standards described above require  $V_{CCO}$  and/or  $V_{REF}$  voltages. These voltages externally and connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

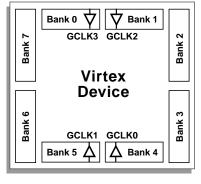

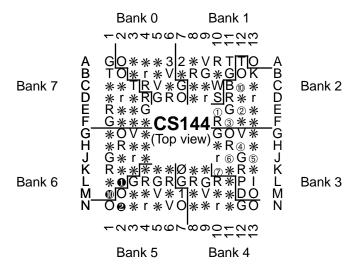

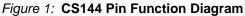

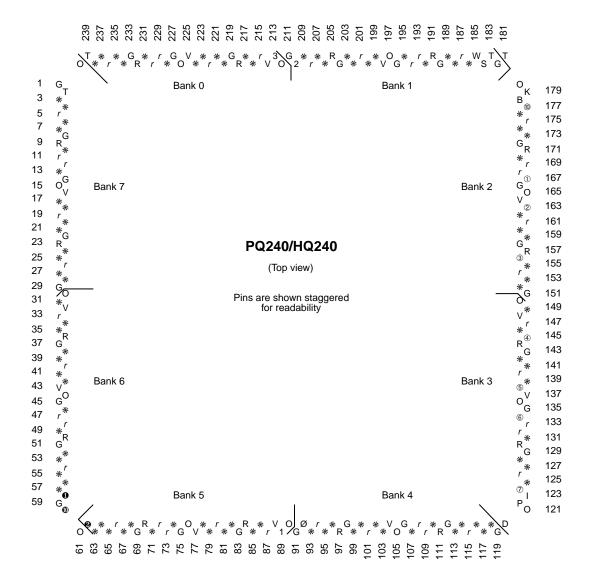

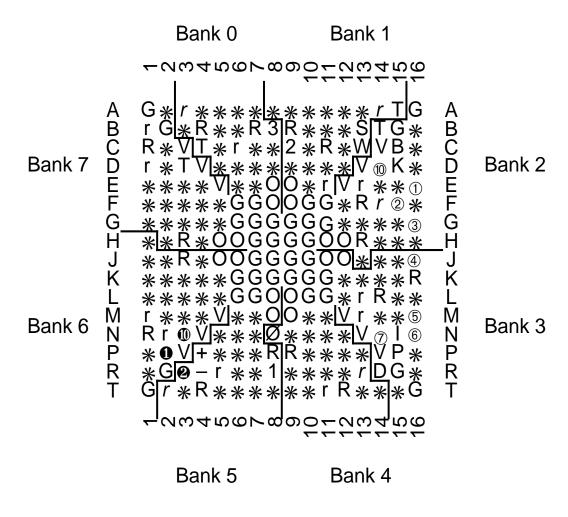

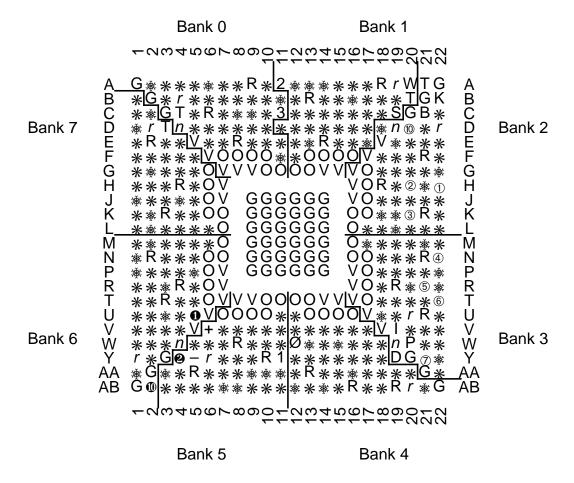

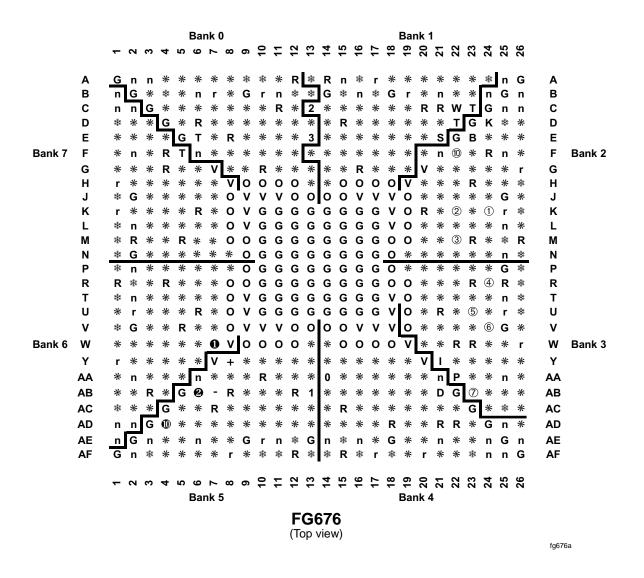

Eight I/O banks result from separating each edge of the FPGA into two banks, as shown in Figure 3. Each bank has multiple  $V_{CCO}$  pins, all of which must be connected to the same voltage. This voltage is determined by the output standards in use.

X8778\_b

Figure 3: Virtex I/O Banks

Within a bank, output standards can be mixed only if they use the same  $V_{CCO}$ . Compatible standards are shown in Table 2. GTL and GTL+ appear under all voltages because their open-drain outputs do not depend on  $V_{CCO}$ .

Table 2: Compatible Output Standards

| V <sub>CCO</sub> | Compatible Standards                               |

|------------------|----------------------------------------------------|

| 3.3 V            | PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL, GTL+ |

| 2.5 V            | SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+              |

| 1.5 V            | HSTL I, HSTL III, HSTL IV, GTL, GTL+               |

Some input standards require a user-supplied threshold voltage,  $V_{\sf REF}$  In this case, certain user-I/O pins are automatically configured as inputs for the  $V_{\sf REF}$  voltage. Approximately one in six of the I/O pins in the bank assume this role.

The V<sub>REF</sub> pins within a bank are interconnected internally and consequently only one V<sub>REF</sub> voltage can be used within each bank. All V<sub>REF</sub> pins in the bank, however, must be connected to the external voltage source for correct operation.

Within a bank, inputs that require  $V_{REF}$  can be mixed with those that do not. However, only one  $V_{REF}$  voltage can be used within a bank. Input buffers that use  $V_{REF}$  are not 5 V tolerant. LVTTL, LVCMOS2, and PCI 33 MHz 5 V, are 5 V tolerant.

The  $V_{CCO}$  and  $V_{REF}$  pins for each bank appear in the device Pinout tables and diagrams. The diagrams also show the bank affiliation of each I/O.

Within a given package, the number of  $V_{\text{REF}}$  and  $V_{\text{CCO}}$  pins can vary depending on the size of device. In larger devices,

more I/O pins convert to  $V_{REF}$  pins. Since these are always a superset of the  $V_{REF}$  pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device if necessary. All the  $V_{REF}$  pins for the largest device anticipated must be connected to the  $V_{REF}$  voltage, and not used for I/O.

In smaller devices, some V<sub>CCO</sub> pins used in larger devices do not connect within the package. These unconnected pins can be left unconnected externally, or can be connected to the V<sub>CCO</sub> voltage to permit migration to a larger device if necessary.

In TQ144 and PQ/HQ240 packages, all V<sub>CCO</sub> pins are bonded together internally, and consequently the same V<sub>CCO</sub> voltage must be connected to all of them. In the CS144 package, bank pairs that share a side are interconnected internally, permitting four choices for V<sub>CCO</sub>. In both cases, the V<sub>REF</sub> pins remain internally connected as eight banks, and can be used as described previously.

# **Configurable Logic Block**

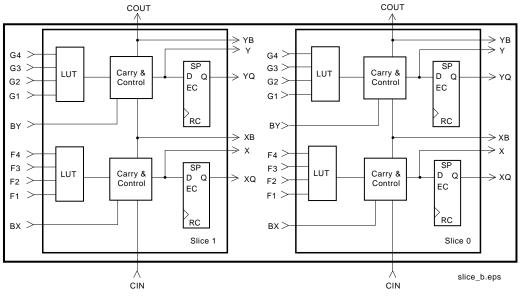

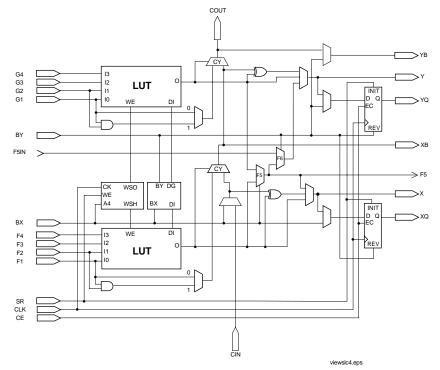

The basic building block of the Virtex CLB is the logic cell (LC). An LC includes a 4-input function generator, carry logic, and a storage element. The output from the function generator in each LC drives both the CLB output and the D input of the flip-flop. Each Virtex CLB contains four LCs, organized in two similar slices, as shown in Figure 4.

Figure 5 shows a more detailed view of a single slice.

In addition to the four basic LCs, the Virtex CLB contains logic that combines function generators to provide functions

of five or six inputs. Consequently, when estimating the number of system gates provided by a given device, each CLB counts as 4.5 LCs.

#### Look-Up Tables

Virtex function generators are implemented as 4-input look-up tables (LUTs). In addition to operating as a function generator, each LUT can provide a 16 x 1-bit synchronous RAM. Furthermore, the two LUTs within a slice can be combined to create a 16 x 2-bit or 32 x 1-bit synchronous RAM, or a 16x1-bit dual-port synchronous RAM.

The Virtex LUT can also provide a 16-bit shift register that is ideal for capturing high-speed or burst-mode data. This mode can also be used to store data in applications such as Digital Signal Processing.

#### Storage Elements

The storage elements in the Virtex slice can be configured either as edge-triggered D-type flip-flops or as level-sensitive latches. The D inputs can be driven either by the function generators within the slice or directly from slice inputs, bypassing the function generators.

In addition to Clock and Clock Enable signals, each Slice has synchronous set and reset signals (SR and BY). SR forces a storage element into the initialization state specified for it in the configuration. BY forces it into the opposite state. Alternatively, these signals can be configured to operate asynchronously. All of the control signals are independently invertible, and are shared by the two flip-flops within the slice.

Figure 4: 2-Slice Virtex CLB

Figure 5: Detailed View of VIrtex Slice

# Additional Logic

The F5 multiplexer in each slice combines the function generator outputs. This combination provides either a function generator that can implement any 5-input function, a 4:1 multiplexer, or selected functions of up to nine inputs.

Similarly, the F6 multiplexer combines the outputs of all four function generators in the CLB by selecting one of the F5-multiplexer outputs. This permits the implementation of any 6-input function, an 8:1 multiplexer, or selected functions of up to 19 inputs.

Each CLB has four direct feedthrough paths, one per LC. These paths provide extra data input lines or additional local routing that does not consume logic resources.

#### Arithmetic Logic

Dedicated carry logic provides fast arithmetic carry capability for high-speed arithmetic functions. The Virtex CLB supports two separate carry chains, one per Slice. The height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a 1-bit full adder to be implemented within an LC. In addition, a dedicated AND gate improves the efficiency of multiplier implementation.

The dedicated carry path can also be used to cascade function generators for implementing wide logic functions.

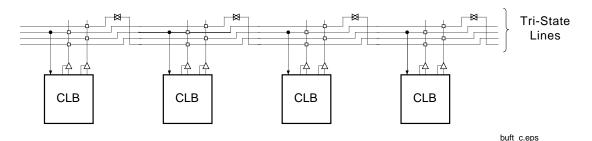

# BUFTs

Each Virtex CLB contains two 3-state drivers (BUFTs) that can drive on-chip busses. See **Dedicated Routing**, page 7. Each Virtex BUFT has an independent 3-state control pin and an independent input pin.

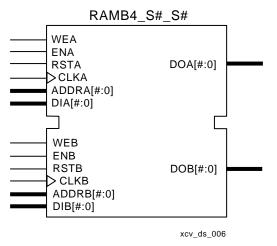

## Block SelectRAM

Virtex FPGAs incorporate several large Block SelectRAM memories. These complement the distributed LUT SelectRAMs that provide shallow RAM structures implemented in CLBs.

Block SelectRAM memory blocks are organized in columns. All Virtex devices contain two such columns, one along each vertical edge. These columns extend the full height of the chip. Each memory block is four CLBs high, and consequently, a Virtex device 64 CLBs high contains 16 memory blocks per column, and a total of 32 blocks.

Table 3 shows the amount of Block SelectRAM memory that is available in each Virtex device.

#### Table 3: Virtex Block SelectRAM Amounts

| Device  | # of Blocks | Total Block SelectRAM Bits |

|---------|-------------|----------------------------|

| XCV50   | 8           | 32,768                     |

| XCV100  | 10          | 40,960                     |

| XCV150  | 12          | 49,152                     |

| XCV200  | 14          | 57,344                     |

| XCV300  | 16          | 65,536                     |

| XCV400  | 20          | 81,920                     |

| XCV600  | 24          | 98,304                     |

| XCV800  | 28          | 114,688                    |

| XCV1000 | 32          | 131,072                    |

Each Block SelectRAM cell, as illustrated in Figure 6, is a fully synchronous dual-ported 4096-bit RAM with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion.

Figure 6: Dual-Port Block SelectRAM

Table 4 shows the depth and width aspect ratios for the Block SelectRAM.

#### Table 4: Block SelectRAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

The Virtex Block SelectRAM also includes dedicated routing to provide an efficient interface with both CLBs and other Block SelectRAMs.

# Programmable Routing Matrix

It is the longest delay path that limits the speed of any worst-case design. Consequently, the Virtex routing architecture and its place-and-route software were defined in a single optimization process. This joint optimization minimizes long-path delays, and consequently, yields the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

Figure 7: Virtex Local Routing

# Local Routing

The VersaBlock provides local routing resources, as shown in Figure 7, providing the following three types of connections.

- Interconnections among the LUTs, flip-flops, and GRM

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

- Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM.

# General Purpose Routing

Most Virtex signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the rows and columns CLBs. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 72 buffered Hex lines route GRM signals to another GRMs six-blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines can be driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are uni-directional.

12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

# I/O Routing

Virtex devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

## **Dedicated Routing**

Some classes of signal require dedicated routing resources to maximize performance. In the Virtex architecture, dedicated routing resources are provided for two classes of signal.

- Horizontal routing resources are provided for on-chip 3-state busses. Four partitionable bus lines are provided per CLB row, permitting multiple busses within a row, as shown in Figure 8.

- Two dedicated nets per CLB propagate carry signals vertically to the adjacent CLB.

Figure 8: BUFT Connections to Dedicated Horizontal Bus Lines

# **Global Routing**

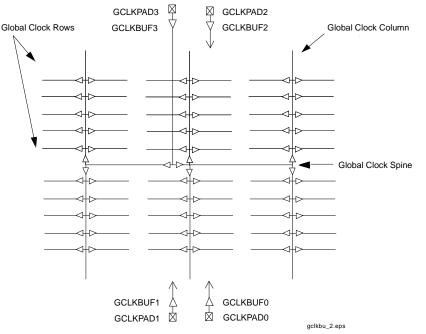

Global Routing resources distribute clocks and other signals with very high fanout throughout the device. Virtex devices include two tiers of global routing resources referred to as primary global and secondary local clock routing resources.

- The primary global routing resources are four dedicated global nets with dedicated input pins that are designed to distribute high-fanout clock signals with minimal skew. Each global clock net can drive all CLB, IOB, and block RAM clock pins. The primary global nets can only be driven by global buffers. There are four global buffers, one for each global net.

- The secondary local clock routing resources consist of 24 backbone lines, 12 across the top of the chip and 12 across bottom. From these lines, up to 12 unique signals per column can be distributed via the 12 longlines in the column. These secondary resources are more flexible than the primary resources since they are not restricted to routing only to clock pins.

# **Clock Distribution**

Virtex provides high-speed, low-skew clock distribution through the primary global routing resources described above. A typical clock distribution net is shown in Figure 9.

Four global buffers are provided, two at the top center of the device and two at the bottom center. These drive the four primary global nets that in turn drive any clock pin.

Four dedicated clock pads are provided, one adjacent to each of the global buffers. The input to the global buffer is selected either from these pads or from signals in the general purpose routing.

Figure 9: Global Clock Distribution Network

## Delay-Locked Loop (DLL)

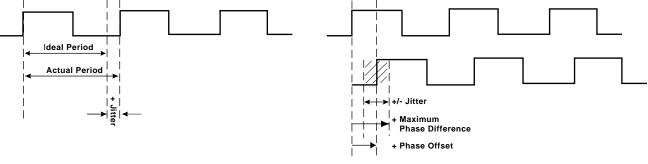

Associated with each global clock input buffer is a fully digital Delay-Locked Loop (DLL) that can eliminate skew between the clock input pad and internal clock-input pins throughout the device. Each DLL can drive two global clock networks. The DLL monitors the input clock and the distributed clock, and automatically adjusts a clock delay element. Clock edges reach internal flip-flops one to four clock periods after they arrive at the input. This closed-loop system effectively eliminates clock-distribution delay by ensuring that clock edges arrive at internal flip-flops in synchronism with clock edges arriving at the input.

In addition to eliminating clock-distribution delay, the DLL provides advanced control of multiple clock domains. The DLL provides four quadrature phases of the source clock, can double the clock, or divide the clock by 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

The DLL also operates as a clock mirror. By driving the output from a DLL off-chip and then back on again, the DLL can be used to de-skew a board level clock among multiple Virtex devices.

In order to guarantee that the system clock is operating correctly prior to the FPGA starting up after configuration, the DLL can delay the completion of the configuration process until after it has achieved lock.

See **DLL Timing Parameters**, page 21 of Module 3, for frequency range information.

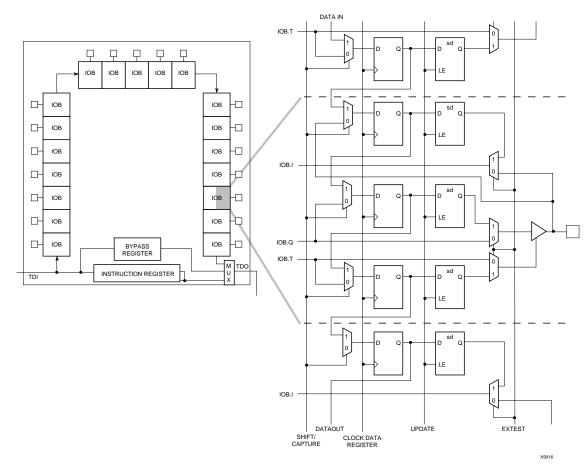

# **Boundary Scan**

Virtex devices support all the mandatory boundary-scan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, and HIGHZ instructions. The TAP also supports two internal scan chains and configuration/readback of the device.The TAP uses dedicated package pins that always operate using LVTTL. For TDO to operate using LVTTL, the V<sub>CCO</sub> for Bank 2 should be 3.3 V. Otherwise, TDO switches rail-to-rail between ground and V<sub>CCO</sub>.

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including un-bonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections.

Table 5 lists the boundary-scan instructions supported inVirtex FPGAs. Internal signals can be captured duringEXTEST by connecting them to un-bonded or unused IOBs.They can also be connected to the unused outputs of IOBsdefined as unidirectional input pins.

Before the device is configured, all instructions except USER1 and USER2 are available. After configuration, all instructions are available. During configuration, it is recommended that those operations using the boundary-scan register (SAMPLE/PRELOAD, INTEST, EXTEST) not be performed. In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

Figure 10 is a diagram of the Virtex Series boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

#### Instruction Set

The Virtex Series boundary scan instruction set also includes instructions to configure the device and read back configuration data (CFG\_IN, CFG\_OUT, and JSTART). The complete instruction set is coded as shown in Table 5.

#### Data Registers

The primary data register is the boundary scan register. For each IOB pin in the FPGA, bonded or not, it includes three bits for In, Out, and 3-State Control. Non-IOB pins have appropriate partial bit population if input-only or output-only. Each EXTEST CAPTURED-OR state captures all In, Out, and 3-state pins.

The other standard data register is the single flip-flop BYPASS register. It synchronizes data being passed through the FPGA to the next downstream boundary scan device. The FPGA supports up to two additional internal scan chains that can be specified using the BSCAN macro. The macro provides two user pins (SEL1 and SEL2) which are decodes of the USER1 and USER2 instructions respectively. For these instructions, two corresponding pins (TDO1 and TDO2) allow user scan data to be shifted out of TDO.

Likewise, there are individual clock pins (DRCK1 and DRCK2) for each user register. There is a common input pin (TDI) and shared output pins that represent the state of the TAP controller (RESET, SHIFT, and UPDATE).

#### **Bit Sequence**

The order within each IOB is: In, Out, 3-State. The input-only pins contribute only the In bit to the boundary scan I/O data register, while the output-only pins contributes all three bits.

From a cavity-up view of the chip (as shown in EPIC), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Figure 11.

BSDL (Boundary Scan Description Language) files for Virtex Series devices are available on the Xilinx web site in the File Download area.

Figure 10: Virtex Series Boundary Scan Logic

| Bit 0 ( TDO end)<br>Bit 1 | Right half of Top-edge IOBs (Right-to-Left)      |

|---------------------------|--------------------------------------------------|

| Bit 2                     | GCLK2<br>GCLK3                                   |

|                           | { Left half of Top-edge IOBs (Right-to-Left)     |

|                           | Left-edge IOBs (Top-to-Bottom)                   |

|                           | M1<br>M0<br>M2                                   |

|                           | Left half of Bottom-edge IOBs (Left-to-Right)    |

|                           | GCLK1<br>GCLK0                                   |

|                           | { Right half of Bottom-edge IOBs (Left-to-Right) |

|                           | DONE<br>PROG                                     |

|                           | Right-edge IOBs (Bottom -to-Top)                 |

| (TDI end)                 | CCLK                                             |

|                           | 990602001                                        |

Figure 11: Boundary Scan Bit Sequence

#### Table 5: Boundary Scan Instructions

| Boundary-Scan<br>Command | Binary<br>Code(4:0) | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan<br>EXTEST operation                     |

| SAMPLE/PRELOAD           | 00001               | Enables boundary-scan<br>SAMPLE/PRELOAD<br>operation          |

| USER 1                   | 00010               | Access user-defined<br>register 1                             |

| USER 2                   | 00011               | Access user-defined<br>register 2                             |

| CFG_OUT                  | 00100               | Access the configuration bus for read operations.             |

| CFG_IN                   | 00101               | Access the configuration bus for write operations.            |

| INTEST                   | 00111               | Enables boundary-scan<br>INTEST operation                     |

| USERCODE                 | 01000               | Enables shifting out<br>USER code                             |

| IDCODE                   | 01001               | Enables shifting out of ID Code                               |

| HIGHZ                    | 01010               | 3-states output pins while<br>enabling the Bypass<br>Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx reserved<br>instructions                               |

## Identification Registers

The IDCODE register is supported. By using the IDCODE, the device connected to the JTAG port can be determined.

The IDCODE register has the following binary format:

vvvv:ffff:fffa:aaaa:aaaa:cccc:cccc1

where

v = the die version number

f = the family code (03h for Virtex family)

a = the number of CLB rows (ranges from 010h for XCV50 to 040h for XCV1000)

c = the company code (49h for Xilinx)

The USERCODE register is supported. By using the USER-CODE, a user-programmable identification code can be loaded and shifted out for examination. The identification code is embedded in the bitstream during bitstream generation and is valid only after configuration.

| FPGA    | IDCODE    |

|---------|-----------|

| XCV50   | v0610093h |

| XCV100  | v0614093h |

| XCV150  | v0618093h |

| XCV200  | v061C093h |

| XCV300  | v0620093h |

| XCV400  | v0628093h |

| XCV600  | v0630093h |

| XCV800  | v0638093h |

| XCV1000 | v0640093h |

#### Table 6: IDCODEs Assigned to Virtex FPGAs

#### Including Boundary Scan in a Design

Since the boundary scan pins are dedicated, no special element needs to be added to the design unless an internal data register (USER1 or USER2) is desired.

If an internal data register is used, insert the boundary scan symbol and connect the necessary pins as appropriate.

# **Development System**

Virtex FPGAs are supported by the Xilinx Foundation and Alliance CAE tools. The basic methodology for Virtex design consists of three interrelated steps: design entry, implementation, and verification. Industry-standard tools are used for design entry and simulation (for example, Synopsys FPGA Express), while Xilinx provides proprietary architecture-specific tools for implementation.

The Xilinx development system is integrated under the Xilinx Design Manager (XDM<sup>™</sup>) software, providing designers

with a common user interface regardless of their choice of entry and verification tools. The XDM software simplifies the selection of implementation options with pull-down menus and on-line help.

Application programs ranging from schematic capture to Placement and Routing (PAR) can be accessed through the XDM software. The program command sequence is generated prior to execution, and stored for documentation.

Several advanced software features facilitate Virtex design. RPMs, for example, are schematic-based macros with relative location constraints to guide their placement. They help ensure optimal implementation of common functions.

For HDL design entry, the Xilinx FPGA Foundation development system provides interfaces to the following synthesis design environments.

- Synopsys (FPGA Compiler, FPGA Express)

- Exemplar (Spectrum)

- Synplicity (Synplify)

For schematic design entry, the Xilinx FPGA Foundation and alliance development system provides interfaces to the following schematic-capture design environments.

- Mentor Graphics V8 (Design Architect, QuickSim II)

- Viewlogic Systems (Viewdraw)

Third-party vendors support many other environments.

A standard interface-file specification, Electronic Design Interchange Format (EDIF), simplifies file transfers into and out of the development system.

Virtex FPGAs supported by a unified library of standard functions. This library contains over 400 primitives and macros, ranging from 2-input AND gates to 16-bit accumulators, and includes arithmetic functions, comparators, counters, data registers, decoders, encoders, I/O functions, latches, Boolean functions, multiplexers, shift registers, and barrel shifters.

The "soft macro" portion of the library contains detailed descriptions of common logic functions, but does not contain any partitioning or placement information. The performance of these macros depends, therefore, on the partitioning and placement obtained during implementation.

RPMs, on the other hand, do contain predetermined partitioning and placement information that permits optimal implementation of these functions. Users can create their own library of soft macros or RPMs based on the macros and primitives in the standard library.

The design environment supports hierarchical design entry, with high-level schematics that comprise major functional blocks, while lower-level schematics define the logic in these blocks. These hierarchical design elements are automatically combined by the implementation tools. Different design entry tools can be combined within a hierarchical design, thus allowing the most convenient entry method to be used for each portion of the design.

# **Design Implementation**

The place-and-route tools (PAR) automatically provide the implementation flow described in this section. The partitioner takes the EDIF net list for the design and maps the logic into the architectural resources of the FPGA (CLBs and IOBs, for example). The placer then determines the best locations for these blocks based on their interconnections and the desired performance. Finally, the router interconnects the blocks.

The PAR algorithms support fully automatic implementation of most designs. For demanding applications, however, the user can exercise various degrees of control over the process. User partitioning, placement, and routing information is optionally specified during the design-entry process. The implementation of highly structured designs can benefit greatly from basic floor planning.

The implementation software incorporates Timing Wizard<sup>®</sup> timing-driven placement and routing. Designers specify timing requirements along entire paths during design entry. The timing path analysis routines in PAR then recognize these user-specified requirements and accommodate them.

Timing requirements are entered on a schematic in a form directly relating to the system requirements, such as the targeted clock frequency, or the maximum allowable delay between two registers. In this way, the overall performance of the system along entire signal paths is automatically tailored to user-generated specifications. Specific timing information for individual nets is unnecessary.

# **Design Verification**

In addition to conventional software simulation, FPGA users can use in-circuit debugging techniques. Because Xilinx devices are infinitely reprogrammable, designs can be verified in real time without the need for extensive sets of software simulation vectors.

The development system supports both software simulation and in-circuit debugging techniques. For simulation, the system extracts the post-layout timing information from the design database, and back-annotates this information into the net list for use by the simulator. Alternatively, the user can verify timing-critical portions of the design using the TRACE<sup>®</sup> static timing analyzer.

For in-circuit debugging, the development system includes a download and readback cable. This cable connects the FPGA in the target system to a PC or workstation. After downloading the design into the FPGA, the designer can single-step the logic, readback the contents of the flip-flops, and so observe the internal logic state. Simple modifications can be downloaded into the system in a matter of minutes.

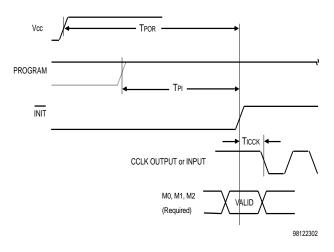

# Configuration

Virtex devices are configured by loading configuration data into the internal configuration memory. Some of the pins used for this are dedicated configuration pins, while others can be re-used as general purpose inputs and outputs once configuration is complete.

The dedicated pins are the mode pins (M2, M1, M0), the configuration clock pin (CCLK), the INIT pin, the DONE pin and the boundary-scan pins (TDI, TDO, TMS, TCK). Depending on the configuration mode chosen, CCLK can be an output generated by the FPGA, or can be generated externally, and provided to the FPGA as an input.

Note that some configuration pins can act as outputs. For correct operation, these pins can require a V<sub>CCO</sub> of 3.3 V to permit LVTTL operation. All the pins affected fall in banks 2 or 3.

After Virtex devices are configured, unused IOBs function as 3-state OBUFTs with weak pull downs. For a more detailed description than that given below, see the XAPP138, Virtex Configuration and Readback.

# **Configuration Modes**

Virtex supports the following four configuration modes.

- Slave-serial mode

- Master-serial mode

- SelectMAP mode

- Boundary-scan mode

The Configuration mode pins (M2, M1, M0) select among these configuration modes with the option in each case of having the IOB pins either pulled up or left floating prior to configuration. The selection codes are listed in Table 7.

Configuration through the boundary-scan port is always available, independent of the mode selection. Selecting the boundary-scan mode simply turns off the other modes. The three mode pins have internal pull-up resistors, and default to a logic High if left unconnected.

| Configuration Mode | M2 | M1 | MO | CCLK Direction | Data Width | Serial D <sub>out</sub> | Configuration Pull-ups |

|--------------------|----|----|----|----------------|------------|-------------------------|------------------------|

| Master-serial mode | 0  | 0  | 0  | Out            | 1          | Yes                     | No                     |

| Boundary-scan mode | 1  | 0  | 1  | N/A            | 1          | No                      | No                     |

| SelectMAP mode     | 1  | 1  | 0  | In             | 8          | No                      | No                     |

| Slave-serial mode  | 1  | 1  | 1  | In             | 1          | Yes                     | No                     |

| Master-serial mode | 1  | 0  | 0  | Out            | 1          | Yes                     | Yes                    |

| Boundary-scan mode | 0  | 0  | 1  | N/A            | 1          | No                      | Yes                    |

| SelectMAP mode     | 0  | 1  | 0  | In             | 8          | No                      | Yes                    |

| Slave-serial mode  | 0  | 1  | 1  | In             | 1          | Yes                     | Yes                    |

#### Table 7: Configuration Codes

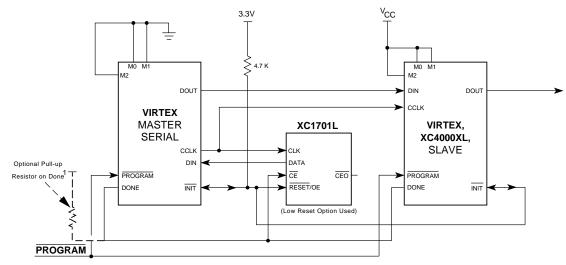

# Slave Serial Mode

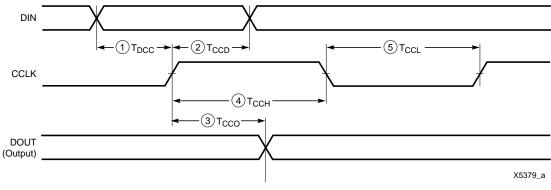

In slave serial mode, the FPGA receives configuration data in bit-serial form from a serial PROM or other source of serial configuration data. The serial bitstream must be setup at the DIN input pin a short time before each rising edge of an externally generated CCLK.

For more information on serial PROMs, see the PROM data sheet at <u>http://www.xilinx.com/partinfo/ds026.pdf</u>.

Multiple FPGAs can be daisy-chained for configuration from a single source. After a particular FPGA has been configured, the data for the next device is routed to the DOUT pin. The data on the DOUT pin changes on the rising edge of CCLK. The change of DOUT on the rising edge of CCLK differs from previous families, but will not cause a problem for mixed configuration chains. This change was made to improve serial-configuration rates for Virtex only chains.

Figure 12 shows a full master/slave system. A Virtex device in slave serial mode should be connected as shown in the third device from the left

Slave-serial mode is selected by applying <111> or <011> to the mode pins (M2, M1, M0). A weak pull-up on the mode pins makes slave serial the default mode if the pins are left unconnected. Figure 13 shows slave-serial configuration timing.

Table 8provides more detail about the characteristicsshown in Figure 13. Configuration must be delayed until theINIT pins of all daisy-chained FPGAs are High.

|      | Description Symbol                    |     | Symbol                               |         | Units    |

|------|---------------------------------------|-----|--------------------------------------|---------|----------|

|      | DIN setup/hold, slave mode            | 1/2 | T <sub>DCC</sub> /T <sub>CCD</sub>   | 5.0/0   | ns, min  |

|      | DIN setup/hold, master mode           | 1/2 | T <sub>DSCK</sub> /T <sub>SCKD</sub> | 5.0 / 0 | ns, min  |

|      | DOUT                                  | 3   | T <sub>CCO</sub>                     | 12.0    | ns, max  |

| CCLK | High time                             | 4   | тссн                                 | 5.0     | ns, min  |

| COLK | Low time                              | 5   | T <sub>CCL</sub>                     | 5.0     | ns, min  |

|      | Maximum Frequency                     |     | F <sub>CC</sub>                      | 66      | MHz, max |

|      | Frequency Tolerance, master mode with |     |                                      | +45%    |          |

|      | respect to nominal                    |     |                                      | -30%    |          |

# Table 8: Master/Slave Serial Mode Programming Switching

Note 1: If none of the Virtex FPGAs have been selected to drive DONE, an external pull-up resistor of 330 Ω should be added to the common DONE line.

xcv\_12\_091499

Figure 12: Master/Slave Serial Mode Circuit Diagram

Figure 13: Slave Serial Mode Programming Switching Characteristics

#### Master Serial Mode

In master serial mode, the CCLK output of the FPGA drives a Xilinx Serial PROM that feeds bit-serial data to the DIN input. The FPGA accepts this data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the rising CCLK edge.

The interface is identical to slave serial except that an internal oscillator is used to generate the configuration clock (CCLK). A wide range of frequencies can be selected for CCLK which always starts at a slow default frequency. Configuration bits then switch CCLK to a higher frequency for the remainder of the configuration. Switching to a lower frequency is prohibited.

The CCLK frequency is set using the ConfigRate option in the bitstream generation software. The maximum CCLK frequency that can be selected is 60 MHz. When selecting a CCLK frequency, ensure that the serial PROM and any daisy-chained FPGAs are fast enough to support the clock rate.

On power-up, the CCLK frequency is 2.5 MHz. This frequency is used until the ConfigRate bits have been loaded when the frequency changes to the selected ConfigRate. Unless a different frequency is specified in the design, the default ConfigRate is 4 MHz.

Figure 12 shows a full master/slave system. In this system, the left-most device operates in master-serial mode. The remaining devices operate in slave-serial mode. The SPROM RESET pin is driven by INIT, and the CE input is driven by DONE. There is the potential for contention on the DONE pin, depending on the start-up sequence options chosen.

Figure 13 shows the timing of master-serial configuration. Master serial mode is selected by a <000> or <100> on the mode pins (M2, M1, M0). Table 8 shows the timing information for Figure 13.

At power-up,  $V_{CC}$  must rise from 1.0 V to  $V_{CC}$  min in less than 50 ms, otherwise delay configuration by pulling PRO-GRAM Low until  $V_{CC}$  is valid.

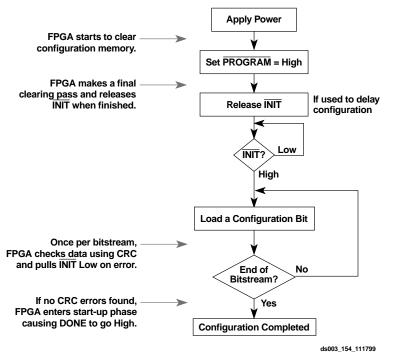

The sequence of operations necessary to configure a Virtex FPGA serially appears in Figure 14.

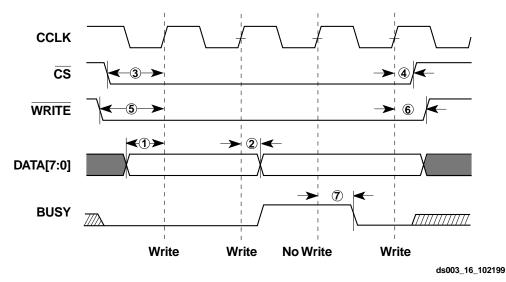

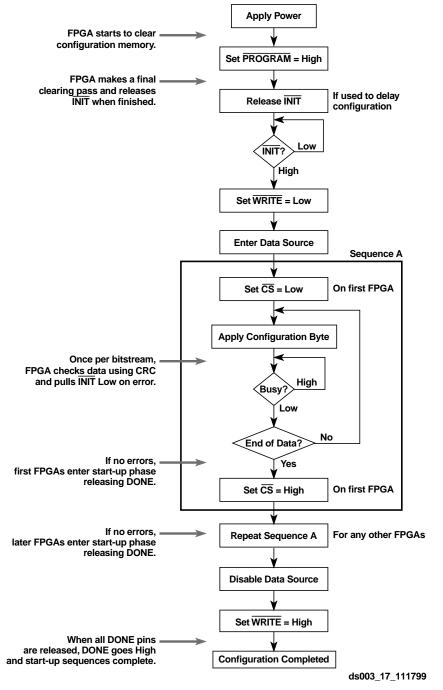

#### SelectMAP Mode

The SelectMAP mode is the fastest configuration option. Byte-wide data is written into the FPGA with a BUSY flag controlling the flow of data.

An external data source provides a byte stream, CCLK, a Chip Select ( $\overline{CS}$ ) signal and a Write signal ( $\overline{WRITE}$ ). If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low.

Data can also be read using the SelectMAP mode. If WRITE is not asserted, configuration data is read out of the FPGA as part of a readback operation.

In the SelectMAP mode, multiple Virtex devices can be chained in parallel. DATA pins (D7:D0), CCLK, WRITE, BUSY, PROG, DONE, and INIT can be connected in parallel between all the FPGAs. Note that the data is organized with the MSB of each byte on pin DO and the LSB of each byte on D7. The  $\overline{CS}$  pins are kept separate, insuring that each FPGA can be selected individually. WRITE should be Low before loading the first bitstream and returned High after the last device has been programmed. Use  $\overline{CS}$  to select the appropriate FPGA for loading the bitstream and sending the configuration data. at the end of the bitstream, deselect the loaded device and select the next target FPGA by setting its CS pin High. A free-running oscillator or other externally generated signal can be used for CCLK. The BUSY signal can be ignored for frequencies below 50 MHz. For details about frequencies above 50 MHz, see XAPP138, Virtex Configuration and Readback. Once all the devices have been programmed, the DONE pin goes High.

Figure 14: Serial Configuration Flowchart

After configuration, the pins of the SelectMAP port can be used as additional user I/O. Alternatively, the port can be retained to permit high-speed 8-bit readback.

Retention of the SelectMAP port is selectable on a design-by-design basis when the bitstream is generated. If retention is selected, PROHIBIT constraints are required to prevent the SelectMAP-port pins from being used as user I/O.

Multiple Virtex FPGAs can be configured using the Select-MAP mode, and be made to start-up simultaneously. To configure multiple devices in this way, wire the individual CCLK, Data, WRITE, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by asserting the  $\overline{CS}$  pin of each device in turn and writing the appropriate data. see Table 9 for SelectMAP Write Timing Characteristics.

|      | Description                         |     | Symbol                                   |           | Units    |

|------|-------------------------------------|-----|------------------------------------------|-----------|----------|

|      | D <sub>0-7</sub> Setup/Hold         | 1/2 | T <sub>SMDCC</sub> /T <sub>SMCCD</sub>   | 5.0 / 1.7 | ns, min  |

|      | CS Setup/Hold                       | 3/4 | T <sub>SMCSCC</sub> /T <sub>SMCCCS</sub> | 7.0 / 1.7 | ns, min  |

| CCLK | WRITE Setup/Hold                    | 5/6 | T <sub>SMCCW</sub> /T <sub>SMWCC</sub>   | 7.0 / 1.7 | ns, min  |

| COLK | BUSY Propagation Delay              | 7   | Т <sub>SMCKBY</sub>                      | 12.0      | ns, max  |

|      | Maximum Frequency                   |     | F <sub>CC</sub>                          | 66        | MHz, max |

|      | Maximum Frequency with no handshake |     | F <sub>CCNH</sub>                        | 50        | MHz, max |

#### Table 9: SelectMAP Write Timing Characteristics

#### Write

Write operations send packets of configuration data into the FPGA. The sequence of operations for a multi-cycle write operation is shown below. Note that a configuration packet can be split into many such sequences. The packet does not have to complete within one assertion of  $\overline{CS}$ , illustrated in Figure 15.

- 1. Assert WRITE and CS Low. Note that when CS is asserted on successive CCLKs, WRITE must remain either asserted or de-asserted. Otherwise an abort will be initiated, as described below.

- 2. Drive data onto D[7:0]. Note that to avoid contention, the data source should not be enabled while  $\overline{CS}$  is Low and  $\overline{WRITE}$  is High. Similarly, while  $\overline{WRITE}$  is High, no more that one  $\overline{CS}$  should be asserted.

- 3. At the rising edge of CCLK: If BUSY is Low, the data is accepted on this clock. If BUSY is High (from a previous write), the data is not accepted. Acceptance will instead occur on the first clock after BUSY goes Low, and the data must be held until this has happened.

- 4. Repeat steps 2 and 3 until all the data has been sent.

- 5. De-assert  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$ .

A flowchart for the write operation appears in Figure 16. Note that if CCLK is slower than  $f_{CCNH}$ , the FPGA will never assert BUSY, In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

Figure 15: Write Operations

Figure 16: SelectMAP Flowchart for Write Operation

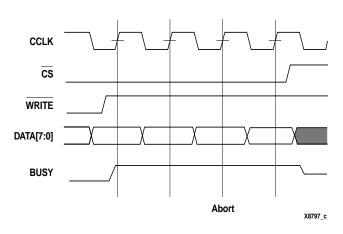

# Abort

During a given assertion of  $\overline{CS}$ , the user cannot switch from a write to a read, or vice-versa. This action causes the current packet command to be aborted. The device will remain BUSY until the aborted operation has completed. Following an abort, data is assumed to be unaligned to word boundaries, and the FPGA requires a new synchronization word prior to accepting any new packets.

To initiate an abort during a write operation, de-assert WRITE. At the rising edge of CCLK, an abort is initiated, as shown in Figure 17.

Figure 17: SelectMAP Write Abort Waveforms

#### Boundary-Scan Mode

In the boundary-scan mode, no non-dedicated pins are required, configuration being done entirely through the IEEE 1149.1 Test Access Port.

Configuration through the TAP uses the CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port (when using TCK as a start-up clock).

- 1. Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the startup sequence

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode is selected by a <101> or 001> on the mode pins (M2, M1, M0).

# **Configuration Sequence**

The configuration of Virtex devices is a three-phase process. First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process.

Configuration is automatically initiated on power-up unless it is delayed by the user, as described below. The configuration process can also be initiated by asserting PROGRAM. The end of the memory-clearing phase is signalled by INIT going High, and the completion of the entire process is signalled by DONE going High. The power-up timing of configuration signals is shown in Figure 18. The corresponding timing characteristics are listed in Table 10. .

#### Figure 18: Power-Up Timing Configuration Signals

#### Table 10: Power-up Timing Characteristics

| Description         | Symbol               | Value | Units           |

|---------------------|----------------------|-------|-----------------|

| Power-on Reset      | T <sub>POR</sub>     | 2.0   | ms, max         |

| Program Latency     | T <sub>PL</sub>      | 100.0 | μ <b>s, max</b> |

| CCLK (output) Delay | Т <sub>ІССК</sub>    | 0.5   | μ <b>s, min</b> |

|                     |                      | 4.0   | μs, max         |

| Program Pulse Width | T <sub>PROGRAM</sub> | 300   | ns, min         |

#### **Delaying Configuration**

$\overline{\text{INIT}}$  can be held Low using an open-drain driver. An open-drain is required since  $\overline{\text{INIT}}$  is a bidirectional open-drain pin that is held Low by the FPGA while the configuration memory is being cleared. Extending the time that the pin is Low causes the configuration sequencer to wait. Thus, configuration is delayed by preventing entry into the phase where data is loaded.

#### Start-Up Sequence

The default Start-up sequence is that one CCLK cycle after DONE goes High, the global 3-state signal (GTS) is released. This permits device outputs to turn on as necessary.

One CCLK cycle later, the Global Set/Reset (GSR) and Global Write Enable (GWE) signals are released. This permits the internal storage elements to begin changing state in response to the logic and the user clock.

The relative timing of these events can be changed. In addition, the GTS, GSR, and GWE events can be made dependent on the DONE pins of multiple devices all going High, forcing the devices to start in synchronism. The sequence can also be paused at any stage until lock has been achieved on any or all DLLs.

# **Data Stream Format**

Virtex devices are configured by sequentially loading frames of data. Table 11 lists the total number of bits required to configure each device. For more detailed information, see application note XAPP151 "Virtex Configuration Architecture Advanced Users Guide".

| Device  | # of Configuration Bits |

|---------|-------------------------|

| XCV50   | 559,200                 |

| XCV100  | 781,216                 |

| XCV150  | 1,040,096               |

| XCV200  | 1,335,840               |

| XCV300  | 1,751,808               |

| XCV400  | 2,546,048               |

| XCV600  | 3,607,968               |

| XCV800  | 4,715,616               |

| XCV1000 | 6,127,744               |

# Readback

The configuration data stored in the Virtex configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents all flip-flops/latches, LUTRAMs, and block RAMs. This capability is used for real-time debugging.

For more detailed information, see application note <u>XAPP138</u>, *Virtex FPGA Series Configuration and Read-back*.

# **Revision History**

| Date  | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/98 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 01/99 | 1.2     | Updated package drawings and specs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 02/99 | 1.3     | Update of package drawings, updated specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 05/99 | 1.4     | Addition of package drawings and specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

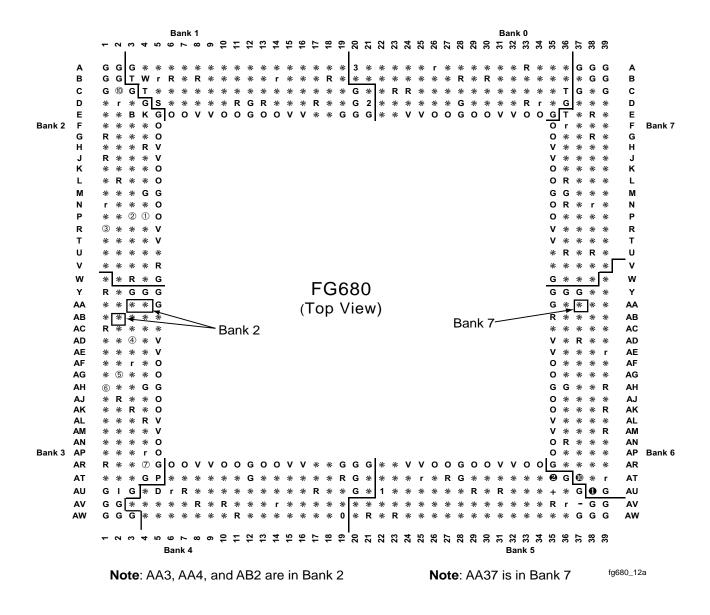

| 05/99 | 1.5     | Replaced FG 676 & FG680 package drawings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 07/99 | 1.6     | Changed Boundary Scan Information and changed Figure 11, Boundary Scan Bit<br>Sequence. Updated IOB Input & Output delays. Added Capacitance info for different I/O<br>Standards. Added 5 V tolerant information. Added DLL Parameters and waveforms and<br>new Pin-to-pin Input and Output Parameter tables for Global Clock Input to Output and<br>Setup and Hold. Changed Configuration Information including Figures 12, 14, 17 & 19.<br>Added device-dependent listings for quiescent currents ICCINTQ and ICCOQ. Updated<br>IOB Input and Output Delays based on default standard of LVTTL, 12 mA, Fast Slew Rate.<br>Added IOB Input Switching Characteristics Standard Adjustments. |

| 09/99 | 1.7     | Speed grade update to preliminary status, Power-on specification and Clock-to-Out Minimums additions, "0" hold time listing explanation, quiescent current listing update, and Figure 6 ADDRA input label correction. Added $T_{IJITCC}$ parameter, changed $T_{OJIT}$ to $T_{OPHASE}$ .                                                                                                                                                                                                                                                                                                                                                                                                    |

| 01/00 | 1.8     | Update to speed.txt file 1.96. Corrections for CRs 111036,111137, 112697, 115479, 117153, 117154, and 117612. Modified notes for Recommended Operating Conditions (voltage and temperature). Changed Bank information for $V_{CCO}$ in CS144 package on p.43.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 01/00 | 1.9     | Updated DLL Jitter Parameter table and waveforms, added Delay Measurement<br>Methodology table for different I/O standards, changed buffered Hex line info and<br>Input/Output Timing measurement notes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 03/00 | 2.0     | New TBCKO values; corrected FG680 package connection drawing; new note about status of CCLK pin after configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 05/00 | 2.1     | Modified "Pins not listed" statement. Speed grade update to Final status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 05/00 | 2.2     | Modified Table 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 09/00 | 2.3     | <ul> <li>Added XCV400 values to table under Minimum Clock-to-Out for Virtex Devices.</li> <li>Corrected Units column in table under IOB Input Switching Characteristics.</li> <li>Added values to table under CLB SelectRAM Switching Characteristics.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10/00 | 2.4     | <ul> <li>Corrected Pinout information for devices in the BG256, BG432, and BG560 packages in Table 18.</li> <li>Corrected BG256 Pin Function Diagram.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 04/01 | 2.5     | <ul> <li>Revised minimums for Global Clock Set-Up and Hold for LVTTL Standard, with DLL.</li> <li>Updated SelectMAP Write Timing Characteristics values in Table 9.</li> <li>Converted file to modularized format. See the Virtex Data Sheet section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Virtex Data Sheet**

The Virtex Data Sheet contains the following modules:

- DS003-1, Virtex 2.5V FPGAs:

<u>Introduction and Ordering Information (Module 1)</u>

- DS003-2, Virtex 2.5V FPGAs: Functional Description (Module 2)

- DS003-3, Virtex 2.5V FPGAs:

DC and Switching Characteristics (Module 3)

- DS003-4, Virtex 2.5V FPGAs:

<u>Pinout Tables (Module 4)</u>

# Virtex<sup>™</sup> 2.5 V Field Programmable Gate Arrays

DS003-3 (v2.5) April 2, 2001

**Product Specification**

# Virtex Electrical Characteristics

# **Definition of Terms**

Data sheets can be designated as Advance or Preliminary. The status of specifications in these data sheets is as follows:

Advance: Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

Unmarked: Data sheets not identified as either Advance or Preliminary are to be considered final.

All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters included are common to popular designs and typical applications. Contact the factory for design considerations requiring more detailed information.

All specifications are subject to change without notice.

# **Virtex DC Characteristics**

# Absolute Maximum Ratings<sup>(1)</sup>

| Symbol             | Description                                   |                    | Units       |    |

|--------------------|-----------------------------------------------|--------------------|-------------|----|

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(2)</sup> |                    | -0.5 to 3.0 | V  |

| V <sub>CCO</sub>   | Supply voltage relative to GND <sup>(2)</sup> |                    | -0.5 to 4.0 | V  |

| V <sub>REF</sub>   | Input Reference Voltage                       |                    | -0.5 to 3.6 | V  |

| N/                 | Input voltage relative to GND <sup>(3)</sup>  | -0.5 to 3.6        | V           |    |

| V <sub>IN</sub>    |                                               | Internal threshold | -0.5 to 5.5 | V  |

| V <sub>TS</sub>    | Voltage applied to 3-state output             |                    | -0.5 to 5.5 | V  |

| V <sub>CC</sub>    | Longest Supply Voltage Rise Time from 1V-2.3  | 75V                | 50          | ms |

| T <sub>STG</sub>   | Storage temperature (ambient)                 |                    | -65 to +150 | °C |

| T <sub>SOL</sub>   | Maximum soldering temp. (10s @ 1/16 in. = 1.5 | +260               | °C          |    |

| TJ                 | Junction temperature                          | Plastic Packages   | +125        | °C |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time can affect device reliability.

2. Power supplies can turn on in any order.

3. For protracted periods (e.g., longer than a day), V<sub>IN</sub> should not exceed V<sub>CCO</sub> by more than 3.6 V.

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

# **Recommended Operating Conditions**

| Symbol                            | Description                                                                              | Min        | Max      | Units    |   |

|-----------------------------------|------------------------------------------------------------------------------------------|------------|----------|----------|---|

| V (1)                             | Input Supply voltage relative to GND, $T_J = 0 \ ^{\circ}C$ to +85 $^{\circ}C$           | Commercial | 2.5 – 5% | 2.5 + 5% | V |

| V <sub>CCINT</sub> <sup>(1)</sup> | Input Supply voltage relative to GND, $T_J = -40^{\circ}C$ to $+100^{\circ}C$ Industrial |            | 2.5 – 5% | 2.5 + 5% | V |

| V (4)                             | Supply voltage relative to GND, $T_J = 0 \ ^{\circ}C$ to +85 $^{\circ}C$                 | Commercial | 1.4      | 3.6      | V |

| V <sub>CCO</sub> <sup>(4)</sup>   | Supply voltage relative to GND, $T_J = -40^{\circ}C$ to $+100^{\circ}C$                  | Industrial | 1.4      | 3.6      | V |

| T <sub>IN</sub>                   | Input signal transition time                                                             |            | 250      | ns       |   |

Notes:

Correct operation is guaranteed with a minimum  $V_{CCINT}$  of 2.375 V (Nominal  $V_{CCINT}$  –5%). Below the minimum value, all delay parameters increase by 3% for each 50-mV reduction in  $V_{CCINT}$  below the specified range. At junction temperatures above those listed as Operating Conditions, delay parameters do increase. Please refer to the TRCE report. Input and output measurement threshold is ~50% of  $V_{CC}$ . 1.

2.

3.

4. Min and Max values for V<sub>CCO</sub> are I/O Standard dependant.

| Symbol             | Description                                                                               | Device  | Min      | Max  | Units |

|--------------------|-------------------------------------------------------------------------------------------|---------|----------|------|-------|

| V <sub>DRINT</sub> | Data Retention V <sub>CCINT</sub> Voltage<br>(below which configuration data can be lost) | All     | 2.0      |      | V     |

| V <sub>DRIO</sub>  | Data Retention V <sub>CCO</sub> Voltage<br>(below which configuration data can be lost)   | All     | 1.2      |      | V     |

| ICCINTQ            | Quiescent V <sub>CCINT</sub> supply current <sup>(1,3)</sup>                              | XCV50   |          | 50   | mA    |

|                    |                                                                                           | XCV100  |          | 50   | mA    |

|                    |                                                                                           | XCV150  |          | 50   | mA    |

|                    |                                                                                           | XCV200  |          | 75   | mA    |

|                    |                                                                                           | XCV300  |          | 75   | mA    |

|                    |                                                                                           | XCV400  |          | 75   | mA    |

|                    |                                                                                           | XCV600  |          | 100  | mA    |

|                    |                                                                                           | XCV800  |          | 100  | mA    |

|                    |                                                                                           | XCV1000 |          | 100  | mA    |

| Iccoq              | Quiescent V <sub>CCO</sub> supply current <sup>(1)</sup>                                  | XCV50   |          | 2    | mA    |

|                    |                                                                                           | XCV100  |          | 2    | mA    |

|                    |                                                                                           | XCV150  |          | 2    | mA    |

|                    |                                                                                           | XCV200  |          | 2    | mA    |

|                    |                                                                                           | XCV300  |          | 2    | mA    |

|                    |                                                                                           | XCV400  |          | 2    | mA    |

|                    |                                                                                           | XCV600  |          | 2    | mA    |

|                    |                                                                                           | XCV800  |          | 2    | mA    |

|                    |                                                                                           | XCV1000 |          | 2    | mA    |

| I <sub>REF</sub>   | V <sub>REF</sub> current per V <sub>REF</sub> pin                                         | All     |          | 20   | μA    |

| ١L                 | Input or output leakage current                                                           | All     | -10      | +10  | μA    |

| C <sub>IN</sub>    | Input capacitance (sample tested) BGA, PQ, HQ, packages                                   | All     |          | 8    | pF    |

| I <sub>RPU</sub>   | Pad pull-up (when selected) @ $V_{in} = 0$ V, $V_{CCO} = 3.3$ V (sample tested)           | All     | Note (2) | 0.25 | mA    |